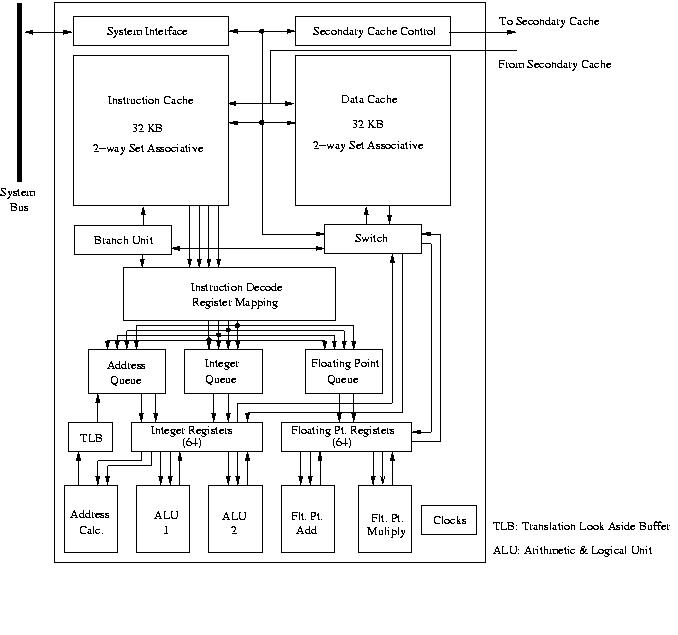

Figure 14: Block diagram of the MIPS R16000 processor.

The essentials of the MIPS R1x000 series of processors have not changed since the introduction of the first in this family, the R10000. The current processor that is at the heart of the SGI Origin3000 series is the R16000. The R16000 is similar to the preceding R14000 except for the clock cycle: this is presently 800 MHz and as such the lowest of all RISC processors employed in High Performance systems. A block diagram of this processor is given in Figure 14.

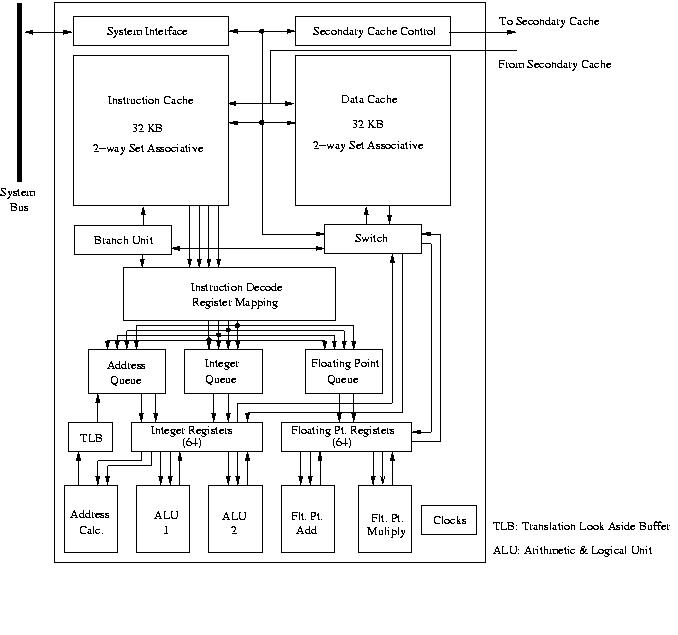

Figure 14: Block diagram of the MIPS R16000 processor.

The R16000 is a typical representative of the modern RISC processors

that are capable of out-of-order and speculative instruction

execution. Like in the Compaq Alpha processor there are two

independent floating-point units for addition and multiplication and,

additionally, two units that perform floating division and square root

operations (not shown in Figure 14). The

latter, however, are not pipelined and with latencies of about 20—30

cycles are relatively slow. In all there are 5 pipelined functional

units to be fed: an address calculation unit which is responsible for

address calculations and loading/storing of data and instructions, two

ALU units for general integer computation and the floating-point add

and multiply pipes already mentioned.

The level 1 instruction and data caches have a moderate size of 32 KB

and are 2-way set-associative. In contrast, the secondary cache can be

very large: up to 16 MB. Both the integer and the floating-point

registers have a physical size of 64 entries, however, 32 of them are

accessible by software while the other half is under direct CPU control

for register re-mapping.

The clock frequency of the MIPS R1x000 processors have always been on

the low side. The first R10000 appeared at a frequency of the 180 MHz

while in the new R16000 the clock cycle is 700 MHz and will slightly rise

during its lifetime. With the initial 700 MHz frequency the theoretical

peak performance is 1.4 Gflop/s. Because of the independent floating-point

units without fused multiply-add capabilities often a fair fraction

of that speed can be realised. There also have been made some

improvements with respect to the earlier chips: the bus speed has

been doubled from 100 MB/s to 200 MB/s and the L1 cache that ran at a

2/3 speed in the predecessor R12000 has been sped up to full speed from

the R14000 on.

The R16000 is built in advanced 0.11 µm technology and it has at the present 800 MHz clock frequency an extremely low power consumption: only 20 Watt, several factors lower than that of the other processors discussed here. SGI keeps the clock frequency intentionally as low as possible to enable to build "dense" systems that can accommodate a large amount of processors in a small volume.

Recently is has become evident that SGI will migrate quickly from its

MIPS platform, the Origin3000 series entirely to the the Itanium-based

Altix family. Therefore it is doubtful whether successors of of the

R16000, the R18000 and the R20000 that originally were projected for mid-2004

and later will ever be realised.