## **Acta Numerica**

http://journals.cambridge.org/ANU

Additional services for **Acta Numerica**:

Email alerts: <u>Click here</u>

Subscriptions: <u>Click here</u>

Commercial reprints: <u>Click here</u>

Terms of use: Click here

## Linear algebra software for large-scale accelerated multicore computing

A. Abdelfattah, H. Anzt, J. Dongarra, M. Gates, A. Haidar, J. Kurzak, P. Luszczek, S. Tomov, I. Yamazaki and A. YarKhan

Acta Numerica / Volume 25 / May 2016, pp 1 - 160

DOI: 10.1017/S0962492916000015, Published online: 23 May 2016

Link to this article: http://journals.cambridge.org/abstract S0962492916000015

#### How to cite this article:

A. Abdelfattah, H. Anzt, J. Dongarra, M. Gates, A. Haidar, J. Kurzak, P. Luszczek, S. Tomov, I. Yamazaki and A. YarKhan (2016). Linear algebra software for large-scale accelerated multicore computing. Acta Numerica, 25, pp 1-160 doi:10.1017/S0962492916000015

Request Permissions: Click here

# Linear algebra software for large-scale accelerated multicore computing\*

A. Abdelfattah, H. Anzt, J. Dongarra, M. Gates, A. Haidar, J. Kurzak P. Luszczek, S. Tomov, I. Yamazaki and A. YarKhan

Innovative Computing Laboratory, University of Tennessee,

1122 Volunteer Boulevard, Suite 203 Claxton,

Knoxville, TN 37996, USA

E-mail: {ahmad,hanzt,dongarra,mgates3,haidar,kurza,

luszczek,tomov,iyamazak,yarkhan}@icl.utk.edu

Many crucial scientific computing applications, ranging from national security to medical advances, rely on high-performance linear algebra algorithms and technologies, underscoring their importance and broad impact. Here we present the state-of-the-art design and implementation practices for the acceleration of the predominant linear algebra algorithms on large-scale accelerated multicore systems. Examples are given with fundamental dense linear algebra algorithms – from the LU, QR, Cholesky, and LDLT factorizations needed for solving linear systems of equations, to eigenvalue and singular value decomposition (SVD) problems. The implementations presented are readily available via the open-source PLASMA and MAGMA libraries, which represent the next generation modernization of the popular LAPACK library for accelerated multicore systems.

To generate the extreme level of parallelism needed for the efficient use of these systems, algorithms of interest are redesigned and then split into well-chosen computational tasks. The task execution is scheduled over the computational components of a hybrid system of multicore CPUs with GPU accelerators and/or Xeon Phi coprocessors, using either static scheduling or light-weight runtime systems. The use of light-weight runtime systems keeps scheduling overheads low, similar to static scheduling, while enabling the expression of parallelism through sequential-like code. This simplifies the development effort and allows exploration of the unique strengths of the various hardware components. Finally, we emphasize the development of innovative linear algebra algorithms using three technologies – mixed precision arithmetic, batched operations, and asynchronous iterations – that are currently of high interest for accelerated multicore systems.

<sup>\*</sup> Colour online for monochrome figures available at journals.cambridge.org/anu.

#### CONTENTS

| 1          | Legacy software packages for dense linear algebra | 2   |

|------------|---------------------------------------------------|-----|

| 2          | New hardware architectures                        | 12  |

| 3          | Dynamic runtime scheduling                        | 16  |

| 4          | LU factorization                                  | 31  |

| 5          | QR factorization                                  | 44  |

| 6          | Cholesky factorization                            | 48  |

| 7          | LDLT decomposition                                | 55  |

| 8          | Eigenvalue and singular value problems            | 64  |

| 9          | Mixed precision algorithms                        | 103 |

| 10         | Batched operations                                | 114 |

| 11         | Sparse linear algebra                             | 138 |

| 12         | Conclusion                                        | 148 |

| References |                                                   | 149 |

# 1. Legacy software packages for dense linear algebra

Over the years, computational physics and chemistry have provided ongoing demand for the ever-increasing performance in hardware and software required to efficiently solve problems in these fields. Fortunately, most of these problems can be translated into solutions for systems of linear equations – the very topic of numerical linear algebra. Seemingly then, a set of efficient linear solvers could be solving important scientific problems for years to come. We also argue that dramatic changes in hardware design, precipitated by the shifting nature of the computer hardware marketplace, has had a continuous effect on numerical linear algebra software, and the extraction of high percentages of peak performance from evolving hardware requires continuous adaptation in software. If the history of linear algebra software's adaptive nature is any indication, then the future holds yet more changes – changes aimed at harnessing the incredible advances of the evolving hardware infrastructure.

# 1.1. The LINPACK library and its implementations

In the 1970s, Fortran was the language for scientific computation: see Figure 1.1. Fortran stores two-dimensional arrays in column-major order (all of the elements of the first column are stored first, then the elements of the second column are stored, and so on). Accessing the array in a row-wise fashion within the matrix could involve successive memory reference to locations separated from each other by a large increment, depending on the size of the declared array. This situation was further complicated by the operating system's use of memory pages to effectively control memory

```

subroutine dgefa(a,lda,n,ipvt,info)

a(k,k) = t

integer Ida,n,ipvt(1),info

10

continue

double precision a(lda,1)

С

double precision t

compute multipliers

С

integer idamax,j,k,kp1,l,nm1

С

t = -1.0d0/a(k,k)

gaussian elimination with partial pivoting

call dscal(n-k,t,a(k+1,k),1)

С

С

row elimination with column indexing

С

nm1 = n - 1

if (nm1 .lt. 1) go to 70

do 30 i = kp1, n

do 60 \text{ k} = 1, \text{ nm} 1

t = a(l,j)

kn1 = k + 1

if (I .eq. k) go to 20

a(l,j) = a(k,j)

С

С

find I = pivot index

a(k,j) = t

С

20

continue

I = idamax(n-k+1,a(k,k),1) + k - 1

call daxpy(n-k,t,a(k+1,k),1,a(k+1,j),1)

ipvt(k) = I

30

С

go to 50

zero pivot implies this column is already triangularized

40

continue

С

info = k

С

if (a(l,k) .eq. 0.0d0) go to 40

50

continue

С

60 continue

interchange if necessary

70 continue

С

ipvt(n) = n

if (I .eq. k) go to 10

if (a(n,n) \cdot eq. 0.0d0) info = n

t = a(l,k)

return

a(l,k) = a(k,k)

end

```

Figure 1.1. LINPACK variant of LU factorization. This is the original FORTRAN 66 code; if LINPACK were written today it would use a modern Fortran standard.

usage. With a large matrix and a row-oriented algorithm in a Fortran environment, an excessive number of page swaps might be generated in the process of running the software. Cleve Moler pointed out this issue in the 1970s (Moler 1972).

In the mid-to-late 1970s, the introduction of vector computer systems marked the beginning of modern supercomputing. These systems offered a performance advantage of at least one order of magnitude over conventional systems of that time. Raw performance was the main, if not the only, selling point of new computing hardware. In the first half of the 1980s the integration of vector systems in conventional computing environments became more important. Only the manufacturers who provided standard programming environments, operating systems, and key applications were successful in earning industrial customers and survived. Performance was mainly increased by improved chip technologies and by producing shared memory multiprocessor systems. These systems were able, in one step, to perform a single operation on a relatively large number of operands stored in vector registers. Expressing matrix algorithms as vector-vector operations was a natural fit for this type of machine (Dongarra, Gustavson and Karp 1984). However, some of the vector designs had a limited ability to load and store the vector registers in main memory. A technique called 'chaining' allowed this limitation to be circumvented by moving data between the

registers *before* accessing main memory. Chaining required recasting linear algebra in terms of matrix–vector operations.

Vector architectures exploit pipeline processing by running mathematical operations on arrays of data in a simultaneous or pipelined fashion. Most algorithms in linear algebra can be easily vectorized. Therefore, in the late 1970s there was an effort to standardize vector operations for use in scientific computations. The idea was to define some simple, frequently used operations and implement them on various systems to achieve portability and efficiency. This package came to be known as the Level 1 Basic Linear Algebra Subprograms (BLAS) or Level 1 BLAS (Lawson, Hanson, Kincaid and Krogh 1979).

The term Level 1 denotes vector-vector operations. As we will see, Level 2 (matrix-vector operations: Hammarling, Dongarra, Du Croz and Hanson 1988), and Level 3 (matrix-matrix operations: Dongarra, Du Croz, Hammarling and Duff 1990) play important roles as well. In the 1970s, dense linear algebra algorithms were implemented in a systematic way by the LIN-PACK project (Dongarra, Bunch, Moler and Stewart 1979). LINPACK is a collection of Fortran subroutines that analyse and solve linear equations and linear least-squares problems. The package solves linear systems whose matrices are general, banded, symmetric indefinite, symmetric positive definite, triangular, and square tridiagonal (only diagonal, super-diagonal, and sub-diagonal are present). In addition, the package computes the QR (matrix Q is unitary or Hermitian and R is upper trapezoidal) and singular value decompositions of rectangular matrices and applies them to least-squares problems. LINPACK uses column-oriented algorithms, which increase efficiency by preserving locality of reference. By column orientation, we mean that the LINPACK code always references arrays down columns, not across rows. This is important since Fortran stores arrays in column-major order. This means that as one proceeds down a column of an array, the memory references proceed sequentially through memory. Thus, if a program references an item in a particular block, the next reference is likely to be in the same block.

The software in LINPACK was kept machine-independent partly through the introduction of the Level 1 BLAS routines. Calling Level 1 BLAS did almost all of the computation. For each machine, the set of Level 1 BLAS would be implemented in a machine-specific manner to obtain high performance. The Level 1 BLAS subroutines DAXPY, DSCAL, and IDAMAX are used in the routine DGEFA.

It was presumed that the BLAS operations would be implemented in an efficient, machine-specific way suitable for the computer on which the subroutines were executed. On a vector computer, this could translate into a simple, single vector operation. This avoided leaving the optimization up to the compiler and explicitly exposing a performance-critical operation. In a sense, then, the beauty of the original code was regained with the use of a new vocabulary to describe the algorithms: the BLAS. Over time, the BLAS became a widely adopted standard and was most likely the first to enforce two key aspects of software: modularity and portability. Again, these are taken for granted today, but at the time they were not. One could have the advantages of the compact algorithm representation and the portability, because the resulting Fortran code was portable.

Most algorithms in linear algebra can be easily vectorized. However, to gain the most out of such architectures, simple vectorization is usually not enough. Some vector computers are limited by having only one path between memory and the vector registers. This creates a bottleneck if a program loads a vector from memory, performs some arithmetic operations, and then stores the results. In order to achieve top performance, the scope of the vectorization must be expanded to facilitate chaining operations together and to minimize data movement, in addition to using vector operations. Recasting the algorithms in terms of matrix—vector operations makes it easy for a vectorizing compiler to achieve these goals.

Thus, as computer architectures became more complex in the design of their memory hierarchies, it became necessary to increase the scope of the BLAS routines from Level 1 to Level 2 to Level 3.

#### 1.2. Implementation in terms of submatrices

RISC (reduced instruction set computing) computers were introduced in the late 1980s and early 1990s. While their clock rates might have been comparable to those of the vector machines, the computing speed lagged behind due to their lack of vector registers. Another deficiency was their creation of a deep memory hierarchy with multiple levels of cache memory to alleviate the scarcity of bandwidth that was, in turn, caused mostly by a limited number of memory banks. The eventual success of this architecture is commonly attributed to the price point and astonishing improvements in performance over time as predicted by Moore's law (Moore 1965). With RISC computers, the linear algebra algorithms had to be redone yet again. This time, the formulations had to expose as many matrix—matrix operations as possible, which guaranteed good cache re-use.

As mentioned before, the introduction in the late 1970s and early 1980s of vector machines brought about the development of another variant of algorithms for dense linear algebra. This variant was centred on the multiplication of a matrix by a vector. These subroutines were meant to give improved performance over the dense linear algebra subroutines in LINPACK, which were based on Level 1 BLAS. In the late 1980s and early 1990s, with the introduction of RISC-type microprocessors (the 'killer micros') and other machines with cache-type memories, we saw the development of LAPACK

(Anderson *et al.* 1999) Level 3 algorithms for dense linear algebra. A Level 3 code is typified by the main Level 3 BLAS, which, in this case, is matrix multiplication (Anderson and Dongarra 1990b).

The original goal of the LAPACK project was to allow linear algebra problems to run efficiently on vector and shared memory parallel processors. On these machines, LINPACK is inefficient because its memory access patterns disregard the multilayered memory hierarchies of the machines, thereby spending too much time moving data instead of doing useful floating-point operations. LAPACK addresses this problem by reorganizing the algorithms to use block matrix operations, such as matrix multiplication, in the innermost loops (see the paper by Anderson and Dongarra 1990a). These block operations can be optimized for each architecture to account for its memory hierarchy, and so provide a transportable way to achieve high efficiency on diverse modern machines.

Here we use the term 'transportable' instead of 'portable' because, for fastest possible performance, LAPACK requires that highly optimized block matrix operations already be implemented on each machine. In other words, the correctness of the code is portable, but high performance is not – if we limit ourselves to a single Fortran source code.

LAPACK can be regarded as a successor to LINPACK in terms of functionality, although it does not use the same function-calling sequences. As such a successor, LAPACK was a win for the scientific community because it could keep LINPACK's functionality while getting improved use out of new hardware.

Most of the computational work in the algorithm from Figure 1.2 is contained in three routines:

- DGEMM matrix-matrix multiplication,

- DTRSM triangular solve with multiple right-hand sides,

- DGETF2 unblocked LU factorization for operations within a block column.

One of the key parameters in the algorithm is the block size, called NB here. If NB is too small or too large, poor performance can result – hence the importance of the ILAENV function, whose standard implementation was meant to be replaced by a vendor implementation encapsulating machine-specific parameters upon installation of the LAPACK library. At any given point of the algorithm, NB columns or rows are exposed to a well-optimized Level 3 BLAS. If NB is 1, the algorithm is equivalent in performance and memory access patterns to LINPACK's version.

Matrix—matrix operations offer the proper level of modularity for performance and transportability across a wide range of computer architectures, including parallel systems with memory hierarchy. This enhanced performance is due primarily to a greater opportunity for re-using data. There are

```

SUBROLITINE DGETRE(M. N. A. LDA. IPIV. INFO)

DO 20 I = 1 MIN( M N ) NR

INFO, LDA, M, N

JB = MIN( MIN( M, N )-J+1, NB )

IPIV(*)

INTEGER

Factor diagonal and subdiagonal blocks and test for exact

DOUBLE PRECISION A( LDA, * )

DOUBLE PRECISION ONE

CALL DGETF2( M-J+1, JB, A( J, J ), LDA, IPIV( J ), IINFO )

PARAMETER

(ONE = 1.0D+0)

Adjust INFO and the pivot indices.

INTEGER

I. IINFO, J. JB, NB

IF( INFO.EQ.0 .AND. IINFO.GT.0 ) INFO = IINFO + J - 1

EXTERNAL DGEMM, DGETF2, DLASWP, DTRSM

DO 10 I = I MIN(M.I + IB-1)

EXTERNAL XERBLA

IPIV(I) = J - 1 + IPIV(I)

INTEGER

10 CONTINUE

ILAENV

EXTERNAL

II AFNV

Apply interchanges to columns 1:J-1.

INTRINSIC

MAX. MIN

CALL DLASWP( J-1, A, LDA, J, J+JB-1, IPIV, 1 )

IF( J+JB.LE.N ) THEN

INFO = 0

IF( M.LT.0 ) THEN

Apply interchanges to columns J+JB:N.

CALL DLASWP( N-J-JB+1, A(1, J+JB), LDA, J, J+JB-1, IPIV, 1 )

INFO = -1

ELSE IF( N.LT.0 ) THEN

Compute block row of U.

CALL DTRSM( 'Left', 'Lower', 'No transpose', 'Unit', JB,

INFO = -2

ELSE IF( LDA.LT.MAX( 1, M ) ) THEN

$

N-J-JB+1, ONE, A(J, J), LDA, A(J, J+JB), LDA)

IF( J+JB.LE.M ) THEN

INFO = -4

END IF

Update trailing submatrix.

IF( INFO.NE.0 ) THEN

CALL DGEMM( 'No transpose', 'No transpose', M-J-JB+1,

CALL XERBLA( 'DGETRF', -INFO )

N-J-JB+1, JB, -ONE, A(J+JB, J), LDA,

$

RETURN

$

A(J, J+JB), LDA, ONE, A(J+JB, J+JB), LDA)

END IF

IF( M.EQ.0 .OR. N.EQ.0 ) RETURN

END IF

NB = ILAENV( 1, 'DGETRF', ' ', M, N, -1, -1 )

20 CONTINUE

IF( NB.LE.1 .OR. NB.GE.MIN( M, N ) ) THEN

END IF

CALL DGETF2( M. N. A. LDA, IPIV, INFO )

RETURN

```

Figure 1.2. LAPACK's LU factorization routine DGETRF using FORTRAN 77.

numerous ways to accomplish this re-use of data to reduce memory traffic and to increase the ratio of floating-point operations to data movement through the memory hierarchy. This improvement can bring a three- to tenfold improvement in performance on modern computer architectures.

The jury is still out concerning the productivity of writing and reading the LAPACK code: How hard is it to generate the code from its mathematical description? The use of vector notation in LINPACK is arguably more natural than LAPACK's matrix formulation. The mathematical formulas that describe algorithms are usually more complex if only matrices are used, as opposed to mixed vector—matrix notation.

#### 1.3. Beyond a single compute node

The traditional design focus for massively parallel processing (MPP) systems was the very high end of performance. In the early 1990s, the symmetric multiprocessing (SMP) systems of various workstation manufacturers, as well as the IBM SP series – which targeted the lower and medium market segments – gained great popularity. Their price/performance ratios were better thanks to the economies of scale associated with larger production numbers, and due to lack of overhead in the design for support of the very large configurations. Due to the vertical integration of performance, it was

no longer economically feasible to produce and focus on the highest end of computing power alone. The design focus for new systems shifted to the market of medium performance systems.

The acceptance of MPP systems, not only for engineering applications but also for new commercial applications (e.g. databases), emphasized different criteria for market success, such as the stability of the system, continuity/longevity of the manufacturer, and price/performance. Thriving in commercial environments became an important endeavour for a successful supercomputer business in the late 1990s. Due to these factors, and the consolidation of the number of vendors in the market, hierarchical systems built with components designed for the broader commercial market replaced homogeneous systems at the very high end of performance. The market-place adopted clusters of SMPs readily, while academic research focused on clusters of workstations and PCs.

At the end of the 1990s, clusters were common in academia but mostly as research objects and not primarily as general-purpose computing platforms for applications. Most of these clusters were of comparable small scale, and as a result the November 1999 edition of the TOP500 (Meuer, Strohmaier, Dongarra and Simon 2011) listed only seven cluster systems. This changed dramatically as industrial and commercial customers started deploying clusters as soon as applications with less stringent communication requirements permitted them to take advantage of the better price/performance ratio. At the same time, all major vendors in the HPC market started selling this type of cluster to their customer base. In November 2004, clusters were the dominant architectures in the TOP500, with 294 systems at all levels of performance. Companies such as IBM and Hewlett-Packard were selling the majority of these clusters, and a large number of them were installed for commercial and industrial customers.

In the early 2000s, clusters built with off-the-shelf components gained more and more attention not only as academic research objects, but also as viable computing platforms for end-users of HPC computing systems. By 2004, these groups of clusters represented the majority of new systems on the TOP500 in a broad range of application areas. One major consequence of this trend was the rapid rise in the utilization of Intel processors in HPC systems. While virtually absent in the high end at the beginning of the decade, Intel processors are now used in the majority of HPC systems. Clusters in the 1990s were mostly self-made systems designed and built by small groups of dedicated scientists or application experts. This changed rapidly as soon as the market for clusters based on PC technology matured. Today, the large majority of TOP500-class clusters are manufactured and integrated by either a few traditional large HPC manufacturers, such as IBM or Hewlett-Packard, or numerous small, specialized integrators of such systems.

In addition, clusters generally still have different uses compared to their more integrated counterparts: clusters are mostly used for capacity computing, while the integrated machines are primarily used for capability computing. The largest supercomputers are used for capability or turnaround computing where the maximum processing power is applied to a single problem. The goal is to solve a larger problem, or to solve a single problem in a shorter period of time. Capability computing enables the solution of problems that cannot otherwise be solved in a reasonable period of time (e.q.,by moving from a two-dimensional to a three-dimensional simulation, using finer grids, or using more realistic models). Capability computing also enables the solution of problems with real-time constraints (e.g. predicting weather). The main figure of merit is time to solution. Smaller or cheaper systems are used for capacity computing, where smaller problems are solved. Capacity computing can be used to enable parametric studies or to explore design alternatives; it is often needed to prepare for more expensive runs on capability systems. Capacity systems will often run several jobs simultaneously. The main figure of merit is sustained performance per unit cost. Traditionally, vendors of large supercomputer systems have learned to provide for the capacity mode of operation as the precious resources of their systems were required to be used as effectively as possible. In contrast, Beowulf clusters (clusters made up of commodity computers linked together via a local area network) mostly use the Linux operating system (a small minority use Microsoft Windows), and these operating systems either lack the tools or the tools lack the maturity to utilize a cluster effectively for capability computing. However, as clusters become both larger and more stable on average, in terms of continuous operation, there is a trend to also use them as computational capability servers.

There are a number of communication networks available for use in clusters. Of course 100 Mb/s Ethernet or Gigabit Ethernet is always possible, which is attractive for economic reasons, but it has the drawback of a high latency ( $\sim 100~\mu s$ ) – the time it takes to send the shortest message. Alternatively, there are, for instance, networks that operate from user space, like InfiniBand. The speeds of these networks are more-or-less on a par with some integrated parallel systems. So, apart from the speed of the processors and of the software that is provided by the vendors of traditional integrated supercomputers, the distinction between clusters and the class of custom capability machines becomes rather small and will, especially with advances of the Ethernet standard into the 100 Gb/s territory with latencies well below 10  $\mu s$ , decrease further in the coming years.

LAPACK was designed to be highly efficient on vector processors, high-performance 'superscalar' workstations, and shared memory multiprocessors. LAPACK can also be used satisfactorily on all types of scalar machines (PCs, workstations, and mainframes). However, LAPACK in its

present form is less likely to give good performance on other types of parallel architectures (e.g. massively parallel single instruction multiple data (SIMD) machines or multiple instruction multiple data (MIMD) distributed memory machines). Instead, the ScaLAPACK effort was intended to adapt LAPACK to these new architectures.

Like LAPACK, the ScaLAPACK routines are based on block-partitioned algorithms in order to minimize the frequency of data movement between different levels of the memory hierarchy. The fundamental building blocks of the ScaLAPACK library are distributed memory versions of the Level 2 and Level 3 BLAS (Choi 1995), and a set of Basic Linear Algebra Communication Subprograms (BLACS: Dongarra and Whaley 1995) for communication tasks that arise frequently in parallel linear algebra computations. In the ScaLAPACK routines, all interprocessor communication occurs within the distributed BLAS and the BLACS, so the source code of the top software layer of ScaLAPACK looks very similar to that of LAPACK.

In order to simplify the design of ScaLAPACK, and because the BLAS routines have proved to be very useful tools outside LAPACK, we chose to build a *parallel BLAS*, or PBLAS (Choi 1995), whose interface is as similar to the BLAS as possible. This decision has permitted the ScaLAPACK code to be quite similar, and sometimes nearly identical, to the analogous LAPACK code.

It was our aim that the PBLAS would provide a distributed memory standard, just as the BLAS provided a shared memory standard. This would simplify and encourage the development of high performance and portable parallel numerical software, as well as provide manufacturers with only a small set of routines to be optimized. The acceptance of the PBLAS requires reasonable compromises between competing goals of functionality and simplicity.

The PBLAS operate on matrices distributed in a two-dimensional block cyclic layout. Because such a data layout requires many parameters to fully describe the distributed matrix, we have chosen a more object-oriented approach and encapsulated these parameters in an integer array called an 'array descriptor'.

By using this descriptor, a call to a PBLAS routine is very similar to a call to the corresponding BLAS routine, as shown in Table 1.1. DGEMM computes  $C = \text{BETA} \times C + \text{ALPHA} \times \text{op}(A) \times \text{op}(B)$ , where op(A) is either A or its transpose depending on TRANSA, op(B) is similar, op(A) is M  $\times$  K, and op(B) is K  $\times$  N. PDGEMM is the same, with the exception of the way submatrices are specified. To pass the submatrix starting at A(IA,JA) to DGEMM, for example, the actual argument corresponding to the formal argument A is simply A(IA,JA). PDGEMM, on the other hand, needs to understand the global storage scheme of A to extract the correct submatrix, so IA and JA must be passed in separately.

| Description of parameter                                                                                         | DGEMM                            | PDGEMM                                           |

|------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------|

| Transpose operator: $A, A^T, A^H$<br>Transpose operator: $B, B^T, B^H$                                           | TRANSA<br>TRANSB                 | TRANSA<br>TRANSB                                 |

| Matrix dimensions: $A \in \mathbb{R}^{M \times K}, B \in \mathbb{R}^{K \times N}, C \in \mathbb{R}^{M \times N}$ | M, N, K                          | M, N, K                                          |

| Input scaling: $\alpha A \times B$                                                                               | ALPHA                            | ALPHA                                            |

| Upper left corner of the matrix: $A_{ia,ja}$                                                                     | A( IA, JA )                      | A, IA, JA                                        |

| Leading dimension of A                                                                                           | LDA                              | $\langle \text{see DESCA} \rangle$               |

| Local memory layout of A                                                                                         | $\langle \text{see LDA} \rangle$ | DESCA                                            |

| Upper left corner of the matrix: $B_{\rm ib,jb}$                                                                 | B(IB, JB)                        | B, IB, JB                                        |

| Leading dimension of B                                                                                           | LDB                              | $\langle \mathrm{see} \; \mathtt{DESCB} \rangle$ |

| Local memory layout of B                                                                                         | $\langle \text{see LDB} \rangle$ | DESCB                                            |

**BETA**

C(IC, JC)

LDC

(see LDC)

**BETA**

C, IC, JC

⟨see DESCC⟩

**DESCC**

Table 1.1. Comparison between parameters of DGEMM and PDGEMM.

#### 1.4. Into the modern era of heterogeneous hardware

Output scaling:  $\beta C$

Leading dimension of C

Local memory layout of C

Upper left corner of the matrix:  $C_{\text{ic.ic.}}$

Clearly, the previous sections were historical in nature. Interestingly, many of the design principles and implementation techniques remain relevant when moving into the era of heterogeneous hardware, which requires unprecedented parallelism and customization of algorithmic choices that play into the particular strengths of the underlying computing hardware. The data locality is still important, especially with the growing disparity between the compute units and the memory hierarchy. Vectorization is still present in the form of short vector instructions such as the SSE, AVX, and AltiVec extensions, as well as warps and half-warps on NVIDIA GPUs. Data distribution comes to the fore when deciding the placement of inputs and outputs of the computational kernels, and now includes the decision of dividing the data between the CPU memory and the accelerator memory. Looking back at the past hardware helps one understand these techniques in a much simpler context.

#### 2. New hardware architectures

#### 2.1. The CORAL machines

Current trends in HPC architectures can best be illustrated by the US Department of Energy's plans for pre-exascale machines, that is, machines with computing capabilities in the range of hundreds of Petaflops, meant to be the stepping stones towards future exascale machines. Under the CORAL collaboration, Oak Ridge National Laboratory (ORNL), Argonne National Laboratory (ANL), and Lawrence Livermore National Laboratory (LLNL) will each deploy powerful pre-exascale supercomputers. These systems will provide the computing power required to meet the mission of the Office of Science and the National Nuclear Security Administration (NNSA) of the US DoE. While NVIDIA GPU-accelerated systems, named Summit and Sierra and based on the IBM OpenPOWER platform, were selected for ORNL and LLNL, an Intel system named Aurora and based on the Xeon Phi platform was selected for ANL. These systems will serve as the models for future exascale designs.

The NVIDIA/IBM-based systems will share a heterogeneous node architecture that tightly integrates IBM POWER CPUs with NVIDIA GPUs using NVIDIA NVLink high-speed coherent interconnect technology. Both machines will be based on IBM Power9 chips, which will emerge just in time for delivery of these systems. The performance and efficiency boost will come from NVIDIA Volta Tesla GPUs, with Mellanox EDR InfiniBand hooking the hybrid Power-Tesla nodes together. The two key features of the Volta GPU are the stacked memory and NVLink interconnect, both of which are important for keeping the processors on both the Power and Tesla components fed. At the same time, the Aurora system at ANL will rely on Intel's HPC scalable system framework, which is a flexible blueprint for developing high-performance, balanced, power-efficient, and reliable systems capable of supporting both compute- and data-intensive workloads. The framework combines next generation Intel Xeon processors and Intel Xeon Phi processors, Intel Omni-Path fabric, silicon photonics, and innovative memory technologies.

#### 2.2. Stacked memory

3D-stacked memories are manufactured by stacking silicon wafers and/or dies and interconnecting them vertically using through-silicon vias (TSVs), so that they behave as a single device to achieve performance improvements with reduced power consumption and smaller footprint than conventional two-dimensional memory. Two leading three-dimensional memory technologies are high bandwidth memory (HBM) and hybrid memory cube (HMC). HBM is a high-performance RAM interface for 3D-stacked DRAM memory

from AMD and Hynix. It is to be used in conjunction with high-performance graphics accelerators and network devices. HBM achieves higher bandwidth while using less power in a substantially smaller form factor than DDR4 or GDDR5. This is achieved by stacking up to eight DRAM dies, including an optional base die with a memory controller, which are interconnected by TSVs and microbumps. The first chip utilizing HBM is AMD Fiji, powering the AMD Radeon R9 Fury X. While the memory bandwidth of the Fury X GPU peaks at 512 GB/s, by 2018 the bandwidth of the NVIDIA Volta is expected to approach 1 TB/s.

HMC is a high-performance RAM interface for TSV-based stacked DRAM memory competing with HBM. HMC promises a 15× speed improvement from DDR3. HMC is backed by several major technology companies including Samsung, Micron Technology, Open-Silicon, ARM, HP, Microsoft, Altera, and Xilinx. Both Intel and IBM target HMC as the memory technology for their future processors. HMC combines TSVs and microbumps to connect multiple dies of memory cell arrays on top of each other. The memory controller is integrated as a separate die. HMC uses standard DRAM cells but it has more data banks than classic DRAM memory of the same size. HMC is intended to greatly increase the amount of memory bandwidth that can be used to feed a processor. This is accomplished by putting the memory as close to the processor as possible to allow what is essentially an extremely wide memory interface, through which an enormous amount of memory bandwidth can be created. The current standard allows for bandwidths as high as 320 GB/s, while IBM advertises bandwidths as high as 230 GB/s for the Power8 CPU.

Multi-channel DRAM (MCDRAM) is a variant of HMC designed just for Intel's processors. Intel and Micron have taken HMC and replaced the standard memory interface with a custom interface better suited for the next generation Xeon Phi, the Knights Landing. The end result is a memory technology that can scale up to 16 GB of RAM while offering up to  $500~\mathrm{GB/s}$  of memory bandwidth.

#### 2.3. NVLink

NVLink is the node integration interconnect for both the Summit and Sierra pre-exascale supercomputers commissioned by the US Department of Energy, enabling NVIDIA GPUs and CPUs such as IBM POWER to access each other's memory quickly and seamlessly. NVLink is an energy-efficient, high-bandwidth path between the GPU and the CPU that uses up to  $3\times$  less energy to move data on the node at bandwidths of 80-200 GB/s, or  $5\times$  to  $12\times$  that of the current PCIe Gen3 x16, delivering faster application performance. Each compute node in Summit will be equipped with over 512 GB of coherent memory, including large-capacity DDR4 system

memory and ultra-fast HBM stacked memory on the GPU. All data will be directly addressable from either the CPU or the GPU, an important feature enabled by the NVLink interconnect.

#### 2.4. Intel Omni-Path and silicon photonics

Intel Omni-Path is Intel's interconnection technology competing with Infini-Band. While the Summit and Sierra systems will have Mellanox's EDR 100 Gb/s InfiniBand networks, The Aurora system will have an Omni-Path network. Starting with the Knights Landing processor, and continuing with Knights Hill, Intel will be integrating their fabric controller on to the processor itself, doing away with the external fabric controller, the space it occupies, and the potential bottlenecks that come from using a discrete fabric controller. Current versions of Omni-Path are running at 100 Gb/s, using the Prairie River chip. Before the delivery of the Aurora machine, it is expected to scale up to at least 200 Gb/s, utilize silicon photonics, and be based on the Wolf River chip.

Silicon photonics is an application of photonic systems which use silicon as an optical medium. Silicon photonic devices can be made using existing semiconductor fabrication techniques, and because silicon is already used as the substrate for most integrated circuits, it is possible to create hybrid devices in which the optical and electronic components are integrated onto a single microchip. Consequently, silicon photonics is being actively researched by many electronics manufacturers including Intel and IBM, as well as by academic research groups, and is seen as a means for keeping on track with Moore's law, by using optical interconnects to provide faster data transfer both between and within microchips.

## 2.5. Hybrid computing

The Summit and Sierra computers put emphasis on hybrid computing. For uncompromising performance, a heterogeneous architecture, coupling powerful latency-optimized processors with highly parallel throughput-optimized accelerators, can significantly outperform non-specialized, homogeneous alternatives. Today's most successful scalable HPC applications distribute data, work across the nodes of a system, and organize algorithms to operate as independently as possible on millions or billions of data elements. However, even simple applications can transition many times between periods of throughput-intensive parallel calculations and sections of latency-sensitive serial operations. The architectural emphasis on parallelism in GPUs leads to optimization for throughput, hiding, rather than minimizing, latency. Support for thousands of threads ensures a ready pool of work in the face of data dependencies in order to sustain performance at a high percent of peak. The memory hierarchy design and technology

thoroughly reflect optimization for throughput performance at minimal energy per bit. By contrast, a latency-optimized CPU architecture drives completely different design decisions. Techniques designed to compress the execution of a single instruction thread into the smallest possible time demand a host of architectural features (e.g. branch prediction, speculative execution, register renaming) that would cost far too much energy to be replicated for thousands of parallel GPU threads, but are entirely appropriate for CPUs. The essence of the heterogeneous computing model is that one size does not fit all. Parallel and serial segments of the workload execute on the best-suited processor – latency-optimized CPU or throughput-optimized GPU – delivering faster overall performance, greater efficiency, and lower energy and cost per unit of computation.

By contrast, the Aurora computer offers a much more homogeneous environment. While the existing Knights Corner (first generation Xeon Phi) is a slot-in coprocessor, that must be paired with a standard Xeon CPU, the next generation Knights Landing will be a standalone processor ('self-hosted'), and so will its successor, Knights Hill, which will power the Aurora. Knights Landing will have up to 16 GB of DRAM, 3D-stacked on-package, providing up to 500 GB/s of memory bandwidth (along with up to 384 GB of DDR4-2400 mainboard memory). It also promises three Teraflops of double precision performance, which is  $3\times$  more than Knights Corner. This jump is thanks to moving from Intel's enhanced Pentium 1 (P54C) x86 cores to the company's modern Silvermont x86 cores, which currently lie at the heart of Intel's Atom processors. All the while, these cores are further modified to incorporate AVX units, allowing AVX-512F operations that provide the bulk Knights Landing's computing power and are a similarly potent upgrade over Knights Corner's more basic 512-bit SIMD units.

## 2.6. Impact on software

The current generation of accelerated machines already have a profound impact on HPC software, and so will the next generation, as the hybrid computing model is here to stay. The challenge comes with the sheer size of the machines (millions of cores), heterogeneity of the architectures (latency-optimized cores and throughput-optimized cores), and complexity of the memory system and data links. Exascale machines will have two to three orders of magnitude of parallelism over petascale computers, with much greater parallelism on nodes than is available today. The bulk-synchronous execution models that dominate today's parallel applications will not scale to this level of parallelism. New algorithms need to be developed that identify and leverage more concurrency and reduce synchronization and communication.

# 3. Dynamic runtime scheduling

#### 3.1. Multithreading in PLASMA

Parallel linear algebra software for multicore architectures (PLASMA) is a numerical software library for solving problems in dense linear algebra on systems of multicore processors (Agullo et al. 2009a). PLASMA offers routines for solving a wide range of problems in dense linear algebra, such as non-symmetric, symmetric and symmetric positive definite systems of linear equations, least-squares problems, singular value problems and eigenvalue problems (currently only symmetric eigenvalue problems). PLASMA solves these problems in real and complex arithmetic and in single and double precision. As of this writing, the majority of such systems are on-chip symmetric multiprocessors with classic super-scalar processors as their building blocks (x86 and the like) augmented with short-vector SIMD extensions (SSE and the like). PLASMA has been designed to supersede LAPACK (Anderson et al. 1999), principally by restructuring the software to achieve much greater efficiency on modern computers based on multicore processors.

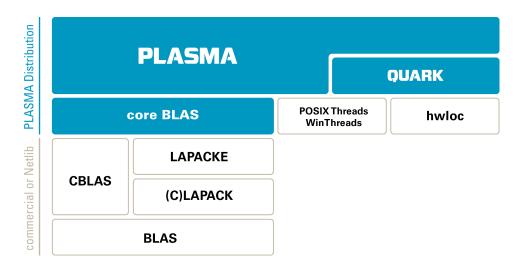

PLASMA is built on top of well-established dense linear algebra software components, and Figure 3.1 shows PLASMA's software stack. PLASMA relies on the collection of Basic Linear Algebra Subroutines (BLAS: Dongarra, Du Croz, Hammarling and Duff 1990), available in many commercial packages (e.q. Intel MKL, AMD ACML, IBM ESSL, Cray LibSci), to extract maximum performance from each individual core. Academic implementations of BLAS are also available (e.g. ATLAS, OpenBLAS). PLASMA utilizes the C interface to BLAS (CBLAS), which is part of most BLAS distributions, but is also available from Netlib in the form of C wrappers to the legacy Fortran interface.<sup>1</sup> PLASMA relies on LAPACK for serial implementations of more complex routines, such as matrix factorizations. Here, PLASMA also utilizes the C interface (LAPACKE), which is distributed by Intel in the MKL software suite, and is also available from Netlib.<sup>2</sup> PLASMA encapsulates all calls to CBLAS and LAPACKE in the core\_blas component, which constitutes the set of all serial building blocks for the parallel algorithms in PLASMA.

The main algorithmic work in PLASMA revolves around efficient multithreading using core\_blas components. Initially, PLASMA was developed using static thread scheduling, but high interest in dynamic task scheduling led to the development of the QUARK scheduler (YarKhan, Kurzak and Dongarra 2011) and gradual introduction of dynamic scheduler routines in PLASMA. PLASMA's statically scheduled routines follow the *single*

www.netlib.org/blas/#\_cblas

<sup>&</sup>lt;sup>2</sup> www.netlib.org/lapack/lapacke.html

Figure 3.1. The software stack of PLASMA, version 2.7.

program multiple data (SPMD) programming paradigm, where each thread relies on its thread ID and the total number of threads in the system to figure out its unique path through the workflow. Synchronization is implemented using shared progress tables and busy waiting. PLASMA's dynamically scheduled routines follow the superscalar programming paradigm, where the code is written sequentially and parallelized at runtime through the analysis of the dataflow between different tasks. As of version 2.7, PLASMA utilizes both types of scheduling, and many routines are available for the two implementations. With the adoption of superscalar scheduling in the OpenMP standard, transition from QUARK to OpenMP is a very likely path forward for PLASMA.

OpenMP is an API that supports multi-platform shared memory multi-processing programming in C, C++, and Fortran, on most processor architectures and operating systems, including Linux, Mac OSX, and Windows. It consists of a set of compiler directives, library routines, and environment variables that influence runtime behaviour. OpenMP is an implementation of multithreading, a method of parallelizing whereby a master thread (a series of instructions executed consecutively) forks a specified number of slave threads, and the system divides a task among them. The threads then run concurrently, with the runtime environment allocating threads to different processors. By default, each thread executes the parallelized section

<sup>&</sup>lt;sup>3</sup> OpenMP Application Program Interface, Version 4.0.

of code independently. Work-sharing constructs can be used to divide a task among the threads so that each thread executes its allocated part of the code. Both task parallelism and data parallelism can be achieved using OpenMP in this way.

The OpenMP Architecture Review Board (ARB) published its first API specifications, OpenMP for Fortran 1.0, in October 1997. In October 1998, the C/C++ standard was released. The year 2000 saw version 2.0 of the Fortran specifications, with version 2.0 of the C/C++ specifications being released in 2002. Version 2.5 is a combined C/C++/Fortran specification that was released in 2005. Up until that point, OpenMP provided mostly fork-join parallelism exemplified by the #parallel for construct. Version 3.0, released in May 2008, included the concept of tasks and the task construct, which drew heavily from the Cilk project (Blumofe et al. 1995) and was quite limited. Version 4.0 of the specification, released in July 2013, adds or improves the following features: support for accelerators, atomics, error handling, thread affinity, tasking extensions, user-defined reduction, SIMD support, and Fortran 2003 support. Most importantly, from the standpoint of PLASMA, the 4.0 standard fully embraces the concept of scheduling work expressed in the form of a Direct Acyclic Graph (DAG) of tasks, also referred to as superscalar scheduling.

Superscalar scheduling relies on the resolution of data hazards/dependencies: read after write (RaW), write after read (WaR), and write after write (WaW). The read after write (RaW) hazard, often referred to as true dependency, is the most common. It defines the relation between a task of writing (creating) the data and the task of reading (consuming) the data. In that case the latter task has to wait until the former task completes. The write after read (WaR) hazard is caused by a situation where a task attempts to write/modify data before a preceding task has finished reading the data. In such a case, the writer has to wait until the reader completes. The dependency is not referred to as a true dependency, because it can be eliminated by renaming (making a copy) of the data. Although the dependency is unlikely to appear often in dense linear algebra, it has been encountered, and it has to be handled by the scheduler to ensure correctness. The write after write (WaW) hazard is caused by a situation where a task attempts to write data before a preceding task has finished writing the data. The final result is expected to be the output of the latter task, but if the dependency is not preserved (and the former task completes after the latter one), incorrect output will result. This is an important dependency in the hardware design of processor pipelines, where resource contention can be caused by a limited number of registers. The situation is, however, quite unlikely for a software scheduler, where the occurrence of the WaW hazard means that some data are produced and overwritten before being consumed. Like the WaR hazard, the WaW hazard can be removed by renaming.

```

#pragma omp parallel

#pragma omp master

POTRF(A);

POTRF(A) {

for (k = 0; k < M; k++) {

#pragma omp task depend(inout:A(k,k)[0:tilesize])

\{ POTF2(A(k,k)); \}

for (m = k+1; m < M; m++) {

#pragma omp task \

depend(in:A(k,k)[0:tilesize]) \setminus

depend (inout: A(m, k) [0: tilesize])

{ TRSM(A(k,k),A(m,k)); }

for (m = k+1; m < M; m++) {

#pragma omp task \

depend (in: A(m, k) [0: tilesize]) \

depend(inout : A(m,m) [0: tilesize])

\{ SYRK(A(m,k),A(m,m)); \}

for (n = k+1; n < m; n++) {

#pragma omp task \

depend (in: A(m,k) [0: tilesize], \

A(n,k)[0:tilesize]

depend(inout : A(m, n) [0 : tilesize])

GEMM(A(m,k), A(n,k), A(m,n)); }

}

}

}

}

```

Figure 3.2. Tile Cholesky algorithm using OpenMP 4.0 tasks with dependencies.

In linear algebra, the Cholesky decomposition or Cholesky factorization is a decomposition of a Hermitian positive definite matrix into the product of a lower triangular matrix and its conjugate transpose. When it is applicable, the Cholesky decomposition is roughly twice as efficient as the LU decomposition for solving systems of linear equations. Figure 3.2 shows the Cholesky factorization expressed using OpenMP 4.0 tasks. The outermost loop iterates over the steps of the factorization. The inner loops iterate over the vertical (m) and horizontal (n) dimensions of the matrix. At each step, a diagonal block A(k,k) is factored (POTRF). Then a triangular solve is used to update all the panel tiles A(m,n) below the diagonal block (TRSM). Finally, all the tiles to the right of the panel (the trailing submatrix) are updated, using a symmetric rank-k update (SYRK) for diagonal tiles A(m,m)and matrix multiplication (GEMM) on the other tiles A(m,n). The #pragma omp task clauses are used to queue tasks for execution and the depend statements are used to specify data dependencies by providing the direction (in/out), the pointer to the data, and the data size.

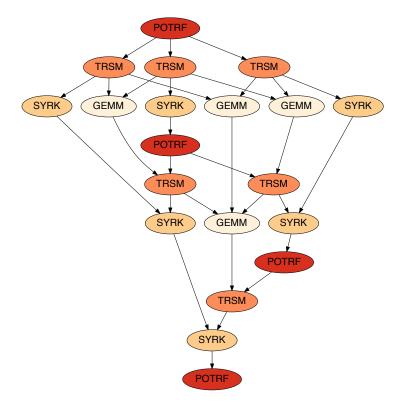

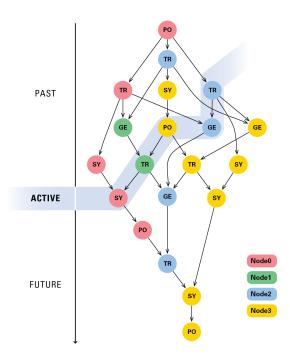

Figure 3.3. The DAG of a  $4\times4$  (tiles) Cholesky factorization.

Figure 3.3 shows the DAG of a  $4 \times 4$  (tiles) Cholesky factorization. Factorization of the first diagonal block (POTRF) unlocks three triangular solves (TRSM) below that block, which in turn unlock three symmetric rank-k updates (SYRK) and three matrix multiplications (GEMM) to the tiles of the trailing submatrix. One of the SYRK operations updates the second diagonal block, which unlocks the factorization of that block (the second POTRF). This process continues until the last diagonal block is factored (the POTRF at the bottom of the DAG), which concludes the factorization of the matrix.

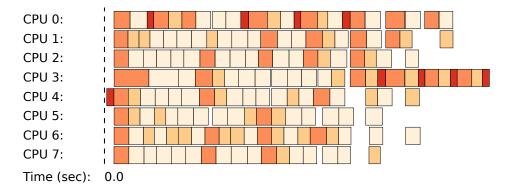

Figure 3.4 shows an execution trace of a larger,  $9 \times 9$  (tiles), Cholesky factorization using eight cores. Here, the first POTRF task unlocks eight TRSM tasks, which in turn unlock many more SYRK and GEMM tasks. Due to dynamic scheduling, there are no clear boundaries between the steps of the factorization. Instead, operations are well pipelined until the cores run out or work at the end of the factorization. The last operations (TRSM, SYRK, POTRF) are serialized due to a chain of dependencies in the DAG.

Figure 3.4. Trace of a  $9 \times 9$  (tiles) Cholesky factorization.

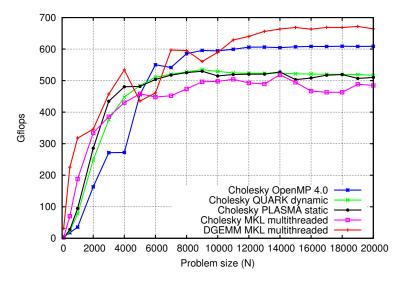

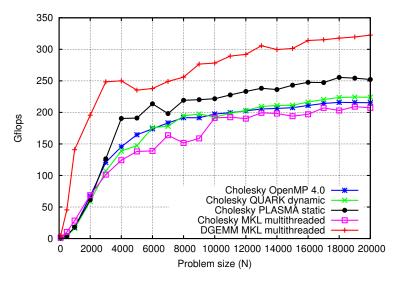

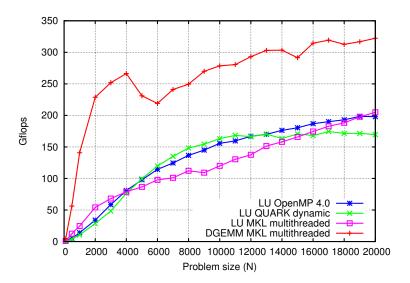

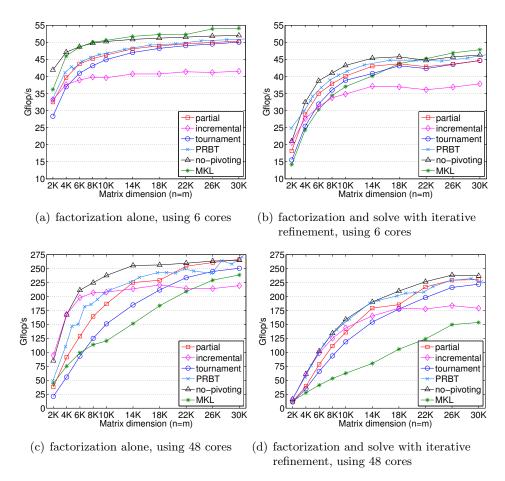

Figure 3.5 compares the performance of different implementations using a dual-socket, 20-core, Intel Haswell system, while Figure 3.6 compares the performance using an eight-socket, 48-core AMD Istanbul system. All codes were compiled using the GCC compiler and linked against the MKL library. In both cases the DGEMM routine from MKL is used as a reference point (basically the upper bound of performance). In the case of the Haswell system, OpenMP delivers performance which matches or exceeds the performance of all the other systems, including: QUARK, PLASMA static scheduling, and the DPOTRF routine from MKL. In the case of the Istanbul system, OpenMP delivers performance better than MKL, almost identical to QUARK and slightly lower than PLASMA static scheduling. In this case, the gap to the static scheduling can probably be closed by further tuning.

A slightly more challenging problem is that of scheduling the LU decomposition. LU decomposition (where 'LU' stands for 'lower upper', and is also called LU factorization) factors a matrix as the product of a lower triangular matrix and an upper triangular matrix. The product sometimes includes a permutation matrix as well. The LU decomposition can be viewed as the matrix form of Gaussian elimination. Computers usually solve square systems of linear equations using the LU decomposition, and it is also a key step when inverting a matrix, or computing the determinant of a matrix. The OpenMP 4.0 implementation of the LU factorization is considerably more complex than the Cholesky factorization. Therefore, Figure 3.7 shows a serial implementation of the LU factorization instead of the actual OpenMP 4.0 implementation. At each step, a block of columns (a panel) is factored (GETRF). Within the panel factorization, partial (row) pivoting is applied and a pivoting pattern is created. That pivoting pattern is

Figure 3.5. Cholesky factorization performance: DPOTRF Intel Xeon E5-2650 v3 (Haswell) 2.3 GHz, 20 cores.

Figure 3.6. Cholesky factorization performance: DPOTRF AMD Opteron 8439 SE (Istanbul) 2.8 GHz, 48 cores (8 sockets, 6 cores).

```

GETRF(A) {

for (k = 0; k < M; k++) {

// panel factorization

GETRF( A(k:M-1,k) );

for (n = k+1; n < N; n++) {

// row interchanges to the right

LASWP (A(k:M-1,n));

// triangular solve at the top

TRSM (A(k,n));

for (m = k+1; m < M; m++) {

// matrix multiply to the right

GEMM(A(m,k), A(k,n), A(m,n));

}

}

for (k = 1; k < M; k++) {

// row interchanges to the left

for (n = 0; n < k-1; n++)

LASWP(A(k:M-1,n));

}

}

```

Figure 3.7. Serial LU factorization.

then applied to the trailing submatrix through a series of row interchanges (LASWP). Then a block of top rows is updated with a triangular solve (TRSM), and finally, all the tiles to the right of the panel are updated, using matrix multiplication (GEMM). At the end of the factorization, row interchanges are applied to the left of each panel.

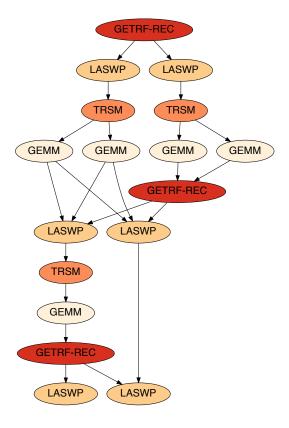

Figure 3.8 shows the DAG of a 3 × 3 (tiles) LU factorization. The first task is the factorization of the first block of columns (panel). Since this is a demanding task, located in the critical path of the algorithm, PLASMA utilizes a very fast, cache-friendly, recursive, multithreaded implementation of this operation, as indicated by the 'REC' postfix in the 'GETRF-REC' label. This task unlocks row interchanges to the right of the panel (LASWP) due to the partial row pivoting technique. They, in turn, unlock triangular solves in the top block of rows (TRSMs), followed by matrix multiplications to update the remainder of the matrix (GEMMs). Two of those GEMM operations update the second panel, and therefore unlock the second GETRF-REC task, and so on. The increased complexity of multithreading the LU factorization stems from the fact that the panel factorization task (GETRF-REC) spans an entire column of tiles, and is internally multithreaded using low-level constructs for synchronization (locks, atomics).

Figure 3.8. The DAG of a  $3\times3$  (tiles) LU factorization.

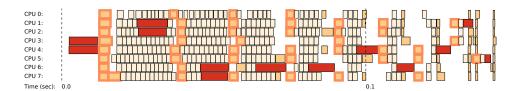

Figure 3.9 shows an execution trace of a larger,  $10 \times 10$  (tiles), LU factorization using eight cores. The first task is the multithreaded GETRF-REC task. In this small example it only uses two threads, and only in the first three steps of the factorization. More threads would be used in a larger case. Completion of the GETRF-REC task unlocks nine LASWP tasks, which in turn unlock nine TRSM tasks, which in turn unlock many more GEMM tasks. Notably, factorization of the second panel can proceed concurrently with the GEMM updates from the first step, factorization of the third panel can proceed concurrently with the GEMM updates from the second step, and so on. Operations are well pipelined until work runs out towards the end of the factorization.

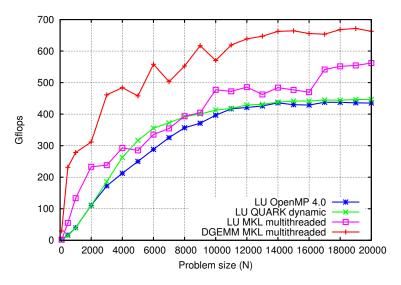

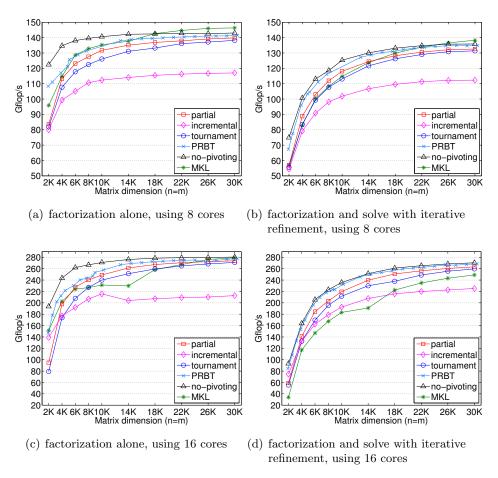

Figure 3.10 compares the performance of different implementations using a dual-socket, 20-core, Intel Haswell system, while Figure 3.11 compares the performance using an eight-socket, 48-core AMD Istanbul system. All codes were compiled using the GCC compiler and linked against the MKL library. In both cases the DGEMM routine from MKL is used as a reference point (the

Figure 3.9. Trace of a  $10 \times 10$  (tiles) LU factorization.

performance upper bound). In the case of the Haswell system, OpenMP delivers slightly lower performance than QUARK and MKL. In the case of the Istanbul system, OpenMP delivers performance almost identical to MKL, and slightly lower than QUARK up to 16 000 and slightly higher beyond that point. OpenMP's performance can, most likely, be improved by further tuning.

In summary, the superscalar scheduling capabilities of OpenMP 4.0 provide many benefits over a proprietary scheduling system. By being language extensions, OpenMP directives produce much more compact and readable codes. By being a standard, OpenMP provides portability to different operating systems, and solves a multitude of lower-level problems, such as thread affinity, etc. At the same time, the GCC implementation provides performance that matches or exceeds that of other similar systems. Therefore, OpenMP seems to be a clear path forward for multithreaded numerical libraries that require sophisticated scheduling, such as PLASMA.

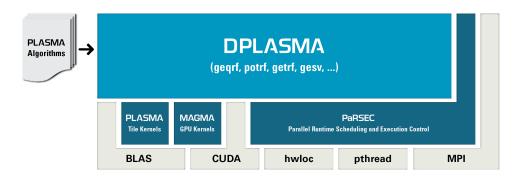

# 3.2. Distributed memory scheduling in DPLASMA

Distributed parallel linear algebra software for multicore architectures (or DPLASMA) is a distributed memory counterpart of PLASMA. DPLASMA contains a subset of PLASMA routines, including routines for solving linear systems of equations and least-squares problems, reductions to condensed form (block-bidiagonal, block-tridiagonal), and a full set of Level 3 BLAS. DPLASMA supports real and complex arithmetic and in single and double precision. DPLASMA targets systems with large numbers of interconnected nodes, where each node may contain multiple sockets of multicore processors and multiple GPU accelerators or Xeon Phi coprocessors. DPLASMA has been designed to supersede ScaLAPACK (Blackford et al. 1997), mainly by restructuring the software to use dataflow runtime scheduling.

DPLASMA is built on top of a few more components than PLASMA. Figure 3.12 shows DPLASMA's software stack. In addition to requiring PLASMA and its subcomponents (BLAS, etc.), DPLASMA also relies on their GPU counterparts (MAGMA, cuBLAS, etc.) The scheduling component of DPLASMA is the parallel runtime scheduler and execution controller

Figure 3.10. LU factorization performance: DGETRF Intel Xeon E5-2650 v3 (Haswell) 2.3 GHz, 20 cores.

Figure 3.11. LU factorization performance: DGETRF AMD Opteron 8439 SE (Istanbul) 2.8 GHz, 48 cores (8 sockets, 6 cores).

Figure 3.12. The software stack of PLASMA, version 1.2.

(PaRSEC), which manages multithreading using Pthreads, message passing using MPI, and accelerator offload using CUDA.

PaRSEC is a generic framework for architecture-aware scheduling and management of micro-tasks on distributed many-core heterogeneous architectures. Workloads are expressed as DAGs of tasks with labelled edges designating data dependencies. DAGs are represented in a compact problemsize independent format that can be queried on-demand to discover data dependencies in a completely distributed fashion. PaRSEC assigns computation threads to the cores, overlaps communications and computations, and uses a dynamic fully distributed scheduler.

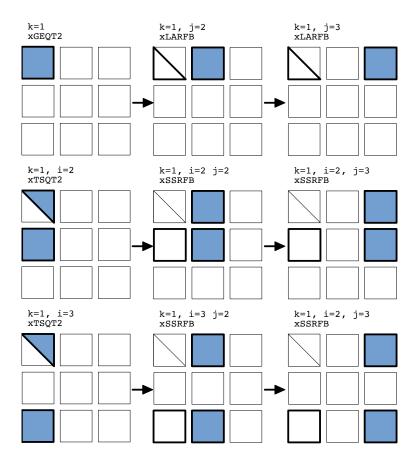

Parametrized task graph (PTG), which is a size-independent representation of a DAG. The notation used in PaR-SEC is called job dependency format (JDF). Figure 3.13 shows the JDF for the Cholesky factorization. The four sections correspond to the four types of tasks used in the factorization: POTRF, TRSM, SYRK, and GEMM. The JDF defines the execution space for each task and the dependencies for all its parameters. Every individual task in the DAG is uniquely identified by a tuple. For instance, the POTRF tasks are identified by the k index in the range from 0 to N-1, while the TRSM tasks are identified by the (m,k)tuple, where m is in the range from 1 to N-1 and k is in the range from 0 to m-1. The POTRF has a single read/write parameter T. In the first step (k == 0) the data come from the memory (A(k, k)). In the followup steps, it comes from the SYRK task of coordinates (k-1,k). After the task executes, the result is forwarded to a set of TRSM tasks of coordinates (k+1..N-1,k), and is also returned to the memory (A(k,k)). In this case forwarding the result from a single source task to multiple destination tasks produces a broadcast pattern.

```

POTRF(k)

k = 0 \dots N-1

RW T \leftarrow (k = 0) ? A(k, k) : T SYRK(k-1, k)

\rightarrow T TRSM(k+1..N-1, k)

-> A(k, k)

TRSM(m, k)

m = 1 \dots N-1

k = 0 ... m-1

READ T \leftarrow T POTRF(k)

C \leftarrow (k = 0) ? A(m, k) : C \times MM(m, k, k-1)

-> A SYRK(k, m)

\rightarrow A GEMM(m, k+1..m-1, k)

\rightarrow B GEMM(m+1..N-1, m, k)

-> A(m, k)

SYRK(k, m)

k = 0 .. N-2

m = k+1 \dots N-1

READ A \leftarrow C TRSM(m, k)

T \leftarrow (k = 0) ? A(m, m) : T SYRK(k-1, m)

\rightarrow (m == k+1) ? T POTRF(m) : T SYRK(k+1, m)

GEMM(m, n, k)

k = 0

.. N-3

m = k+2 \dots N-1

n = k+1 \dots m-1

READ A <- C TRSM(m, k)

READ B \leftarrow C TRSM(n, k)

C \leftarrow (k = 0) ? A(m, n) : C \times MM(m, n, k-1)

\rightarrow (n == k+1) ? C TRSM(m, n) : C GEMM(m, n, k+1)

```

Figure 3.13. Tile Cholesky algorithm expressed using the JDF notation.

Figure 3.14 shows the principles of PaRSEC execution using the DAG of the Cholesky factorization as an example. While the tasks are statically partitioned to nodes, the execution proceeds dynamically by only activating a small portion of the DAG at a time. Execution is asynchronous and communication is hidden, to the best ability of the hardware (*i.e.*, MPI messages and PCI transfers take place while CPU cores and GPU devices are occupied with useful work, given that the code is rich enough in computation to hide the communication). For efficient management of the memories of multiple GPUs, PaRSEC implements its own GPU memory allocator and applies the replacement policy if memory is exhausted. Currently, PaRSEC applies the *least recently used* (LRU) policy. More sophisticated approaches are possible.

Figure 3.14. DAG execution in PaRSEC.

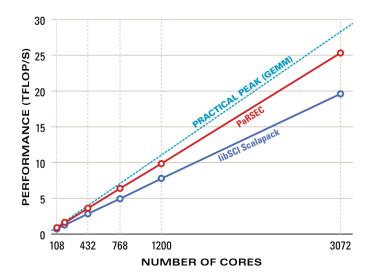

Figure 3.15 compares the performance of PaRSEC to ScaLAPACK, and the theoretical peak when executing the Cholesky factorization in double precision (DPOTRF) on a Cray XT5 system, using up to 3072 CPU cores. It is a weak scaling comparison (i.e., the size of the matrix grows as the core count grows, such that the data size per core remains constant). The Cray implementation of ScaLAPACK is used (LibSci). While LibSci's performance approaches 20 Tflops, PaRSEC's performance crosses 25 Tflops, an improvement of  $\sim 25\%$ . At the same time, PaRSEC gets within 10% of the theoretical peak.

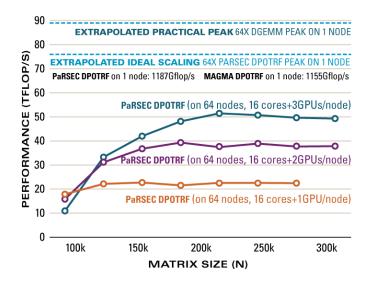

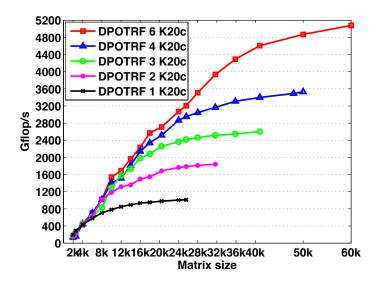

Figure 3.16 shows the performance of Parsec executing the DPOTRF routine on a hybrid system, with 64 nodes including three NVIDIA GPUs per node. Performance is shown using a single GPU per node, two GPUs per node, and all three GPUs per node. When using all 192 GPUs, performance of 50 Gflops is achieved for a matrix of size 200 000.

Figure 3.15. Cholesky factorization performance: DPOTRF Cray XT5 (Kraken).

Figure 3.16. Cholesky factorization performance: distributed hybrid DPOTRF Keeneland 64 nodes (1024 cores, 192 M2090 GPUs, InfiniBand 20G).

# 4. LU factorization

Gaussian elimination has a long history that can be traced back some 2000 years (Great 2011). Today, dense systems of linear equations have become a critical cornerstone for some of the most compute-intensive ap-A sampling of domains using dense linear equations include fusion reactor modelling (Jaeger et al. 2006), aircraft design (Quaranta and Drikakis 2009), acoustic scattering (Bendali, Boubendir and Fares 2007), antenna design, and radar cross-section studies (Zhang et al. 2008). Simulating fusion reactors, for instance, generates dense systems that exceed half a million unknowns, which are solved using LU factorization (Barrett et al. 2010). Many dense linear systems arise from the solution of boundary integral equations via boundary element methods (Edelman 1993), variously called the method of moments in electromagnetics (Harrington 1990), and the panel method in fluid dynamics (Hess 1990). These methods replace a sparse three-dimensional problem of  $O(n^3)$  unknowns with a dense twodimensional problem of  $O(n^2)$  unknowns. Any improvement in the time to solution for dense linear systems has a direct impact on the execution time of these applications.

## 4.1. Algorithms

# 4.1.1. Partial pivoting

The LAPACK block LU factorization is the main point of reference here, and the LAPACK naming convention is followed. The initial 'D' in names denotes double precision routines. The LU factorization of a matrix A has the form

$$PA = LU$$

,

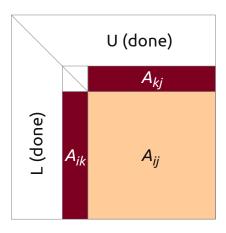

where L is a unit lower triangular matrix, U is an upper triangular matrix, and P is a permutation matrix. The LAPACK algorithm proceeds in the following steps. Initially, a set of  $n_b$  columns (the panel) is factored and a pivoting pattern is produced (implemented by the DGETF2 routine). Then the elementary transformations, resulting from the panel factorization, are applied in a block fashion to the remaining part of the matrix (the trailing submatrix). This involves swapping up to  $n_b$  rows of the trailing submatrix (DLASWP), according to the pivoting pattern, application of a triangular solve with multiple right-hand sides to the top  $n_b$  rows of the trailing submatrix (DTRSM), and finally application of matrix multiplication of the form  $A_{ij} \leftarrow A_{ij} - A_{ik} \times A_{kj}$  (DGEMM), where  $A_{ik}$  is the panel without the top  $n_b$  rows,  $A_{kj}$  is the top  $n_b$  rows of the trailing submatrix, and  $A_{ij}$  is the trailing submatrix without the top  $n_b$  rows. Then the procedure is applied repeatedly, descending down the diagonal of the matrix: see Figure 4.1.

Figure 4.1. The block LU factorization (Level 3 BLAS algorithm of LAPACK).

The block algorithm is described in detail in section 2.6.3 of the book by Demmel (1997).

Instead of the Level 2 BLAS panel factorization (DGETF2) of LAPACK, we use a recursive partial pivoting panel factorization, which uses Level 3 BLAS operations. For a panel of k columns, the algorithm recursively factors the left k/2 columns, updates the right k/2 columns with DLASWP, DTRSM, and DGEMM, then recursively factors the right k/2 columns, and finally applies swaps to the left k/2 columns with DLASWP. The recursion terminates at a single column, where it simply searches for the maximum pivot, swaps elements, and scales the column by the pivot. Parallelism is introduced by splitting the panel into p block rows, which are assigned to different processors.

## 4.1.2. Incremental pivoting

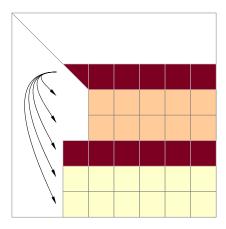

The most performance-limiting aspect of Gaussian elimination with partial pivoting is the panel factorization operation. First, it is an inefficient operation, usually based on a sequence of calls to Level 2 BLAS. Second, it introduces synchronization, by locking an entire panel of the matrix at a time. Therefore, it is desirable to split the panel factorization into a number of smaller, finer-granularity operations, which is the basic premise of the *incremental pivoting* implementation, also known in the literature as the *tile LU* factorization.

In this algorithm, instead of factoring the panel one column at a time, the panel is factored one tile at a time. The operation proceeds as follows. First the diagonal tile is factored using the standard LU factorization procedure. Then the factored tile is combined with the tile directly below it and

Figure 4.2. Incremental LU factorization.

factored. Then the refactored diagonal tile is combined with the next tile and factored again. The algorithm descends down the panel until the bottom of the matrix is reached. At each step, the standard partial pivoting procedure is applied to the tiles being factored. Also, at each step, all the tiles to the right of the panel are updated with the elementary transformations resulting from the panel operations: see Figure 4.2. This way of pivoting is basically the idea of pairwise pivoting applied at the level of tiles, rather than individual elements. The main benefit comes from the fact that updates of the trailing submatrix can proceed alongside panel factorizations, leading to a very efficient parallel execution, where multiple steps of the algorithm are smoothly pipelined.

A straightforward implementation of incremental pivoting incurs more floating-point operations than partial pivoting. To reduce this additional cost, a second level of blocking, called *inner blocking*, is used within each tile (Joffrain, Quintana-Orti and van de Geijn 2006, Buttari, Langou, Kurzak and Dongarra 2009). The total cost to factor an  $n \times n$  matrix is

$$\frac{2}{3}n^3\left(1+\frac{i_b}{2n_b}\right)+O(n^2),$$

where  $n_b$  is the tile size and  $i_b$  is the inner blocking size. A small value for  $i_b$  decreases the flops but may hurt the efficiency of Level 3 BLAS operations, so  $n_b$  and  $i_b$  should be chosen to offer the best compromise between extra operations and BLAS efficiency.

With  $n_b = 1$ , incremental pivoting reduces to pairwise pivoting, hence the stability of incremental pivoting is assumed to be the same as pairwise pivoting (Joffrain *et al.* 2006). For pairwise pivoting, the growth factor

bound is  $4^{n-1}$ . Trefethen and Schreiber (1990) observed an average growth factor of n for  $n \leq 1024$ , but more recently, Grigori, Demmel and Xiang (2011) observed an average growth factor > n for  $n \geq 4096$ , leaving the question of stability open for large n.

## 4.1.3. Tournament pivoting

Classic approaches to the panel factorization with partial pivoting communicate asymptotically more than the established lower bounds (Demmel, Grigori, Hoemmen and Langou 2008a). The basic idea of communication-avoiding LU is to minimize communication by replacing the pivot search performed at each column with a block reduction of all the pivots together. This is done thanks to a new pivoting strategy referred to as tournament pivoting, which performs extra computations and is shown to be stable in practice. Tournament pivoting factors the panel in two steps. First, using a tournament selection, it identifies rows that can be used as good pivots for the factorization of the whole panel. Second, it swaps the selected pivot rows to the top of the panel, and then factors the entire panel without pivoting. With this strategy, the panel is efficiently parallelized, and the communication is provably minimized.

Figure 4.3 presents the first step of tournament pivoting for a panel W using a binary tree for the reduction operation. First, the panel is partitioned into  $p_r$  blocks, that is,  $W = [W_{00}, W_{10}, \ldots, W_{p_r-1,0}]$ , where  $W_{ij}$  represents the block owned by thread i at step j of the reduction operation. Figure 4.3 shows an example with  $p_r = 4$ .

At the first step of the reduction operation, each thread, i, applies Gaussian elimination with partial pivoting to its block,  $W_{i0}$ ; then the resulting permutation matrix  $P_{i0}$  is applied to the original unfactored block,  $W_{i0}$ , and the first  $n_b$  rows of the permuted block  $P_{i0}W_{i0}$  are selected as pivot candidates. These first pivot candidates represent the leaves of the reduction tree. At each node of the tree, the pivot candidates of two child nodes are merged on top of each other, and Gaussian elimination with partial pivoting is applied on the merged block. The resulting permutation matrix is then applied on the original unfactored merged block and the first  $n_b$  rows are selected as new pivot candidates. By using a binary tree, this step is repeated  $\log_2 p_r$  times. The pivots obtained at the root of the tree are then considered to be good pivots for the whole panel. Once these pivots are permuted to the top of the panel, each thread applies Gaussian elimination without partial pivoting to its block,  $W_{i0}$ .

The example presented in Figure 4.3 uses a binary tree with two tiles reduced together at each level, but any reduction tree can be used, depending on the underlying architecture. The tournament pivoting implementation in PLASMA, used for experiments in this section, reduces four tiles at each

Figure 4.3. Example of tournament pivoting with  $p_r = 4$  processors, using a binary tree for the reduction operation.

level. This number of tiles is chosen because it gives a good ratio of kernel efficiency over one single core, relative to the time spent to perform the factorization of the subset.

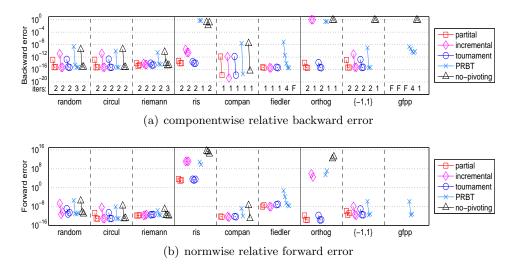

For tournament pivoting, the best growth factor bound proved so far is  $2^{nH}$ , where H is the height of the reduction tree. With a binary tree,  $H = \log_2 p_r$ , so the bound is  $p_r^n$ . However, Grigori et al. (2011) have never observed a growth factor as large as  $2^{n-1}$ , even for pathological cases such as the Wilkinson matrix (Wilkinson 1988), and they conjecture that the upper bound is the same as partial pivoting,  $2^{n-1}$ . They observed an average growth factor of  $1.5n^{2/3}$ , independent of p. Our experiments in Section 4.2.3 confirm that tournament pivoting is as stable as partial pivoting in practice.

# 4.1.4. Random butterfly transform

As an alternative to pivoting, the partial random butterfly transformation (PRBT) preconditions the matrix as  $A_r = W^T A V$ , such that, with probability close to 1, pivoting is unnecessary. This technique was proposed by Parker (1995b) and later adapted by Baboulin, Dongarra, Herrmann and Tomov (2013) to reduce the computational cost of the transformation.

# **Algorithm 1** Solving Ax = b using PRBT.

- $1 \quad A_r = W^T A V$

- 2 factor  $A_r = LU$  without pivoting

- 3  $y = U \setminus (L \setminus (W^T b))$

- $4 \quad x = Vy$

An  $n \times n$  butterfly matrix is defined as

$$B^{(n)} = \frac{1}{\sqrt{2}} \begin{bmatrix} R & S \\ R & -S \end{bmatrix},$$

where R and S are random diagonal, non-singular matrices. W and V are recursive butterfly matrices of depth d, defined by

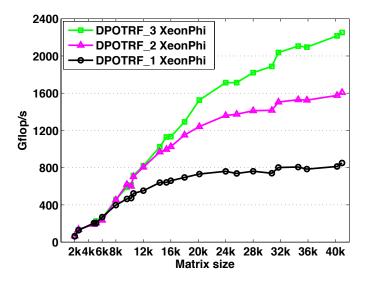

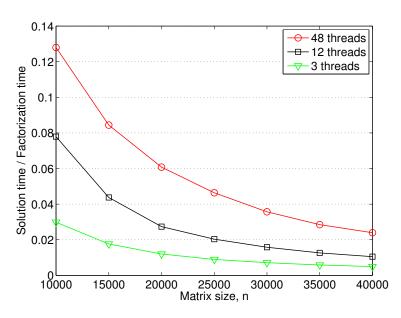

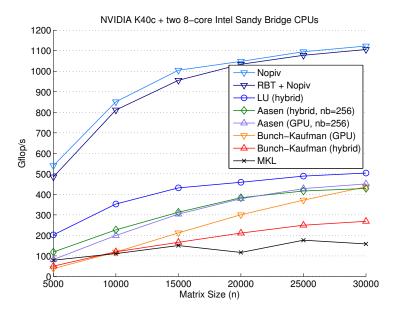

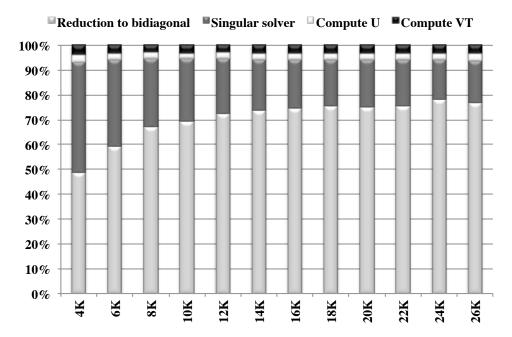

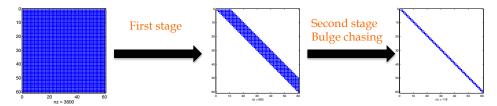

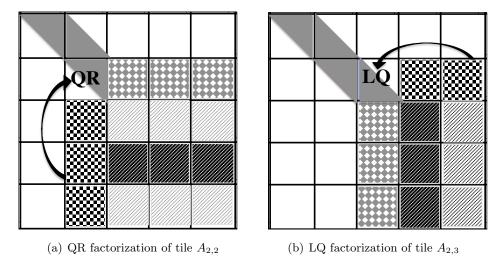

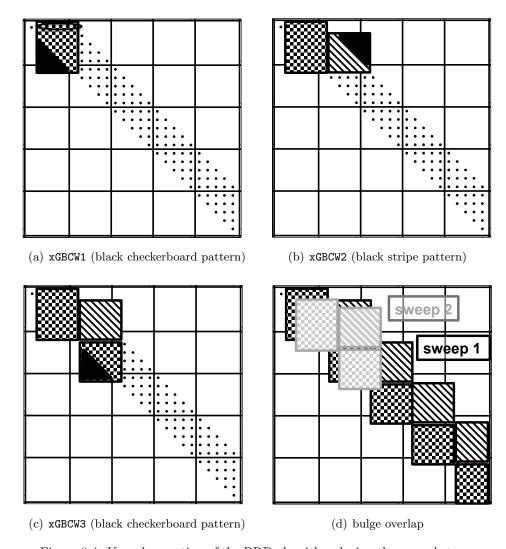

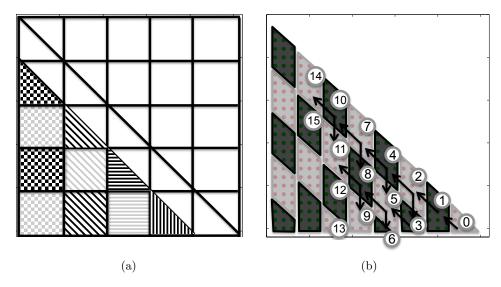

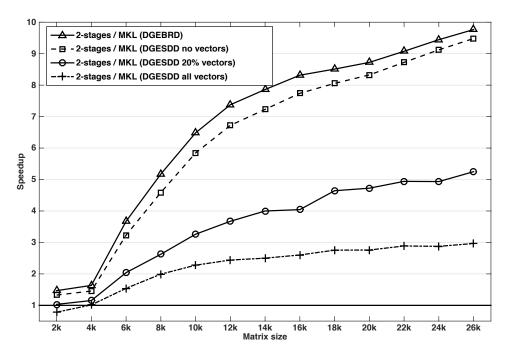

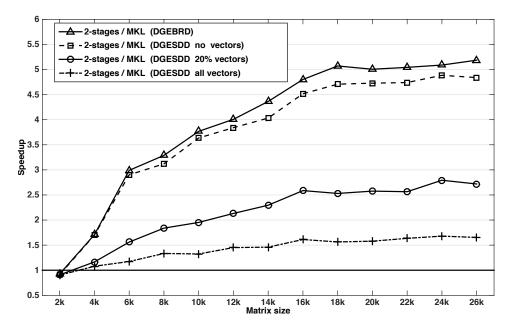

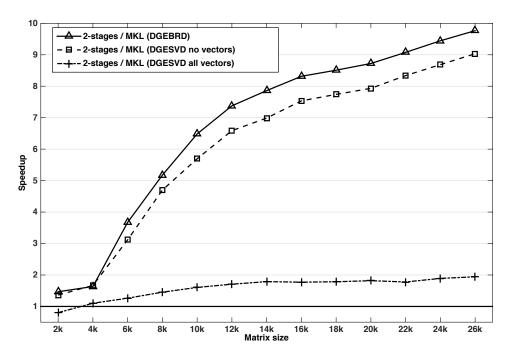

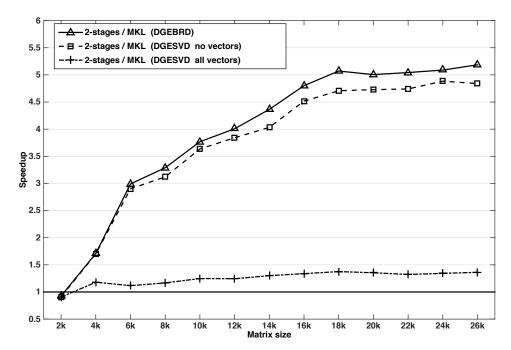

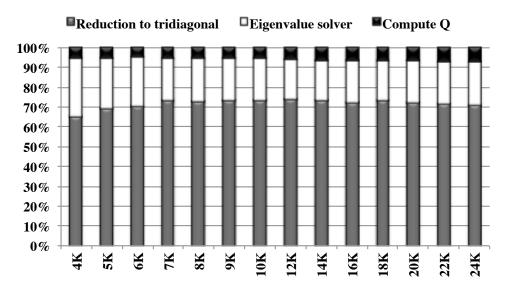

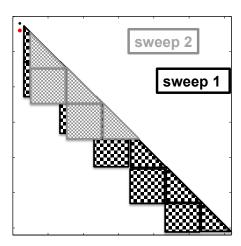

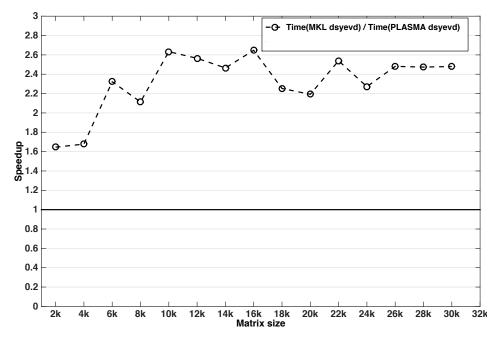

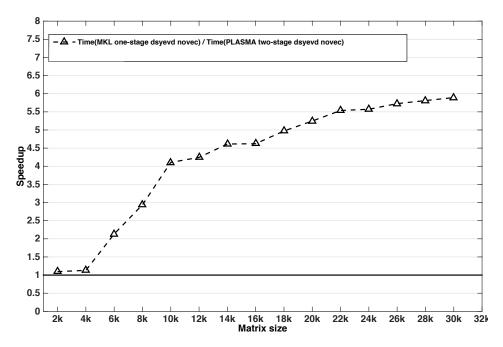

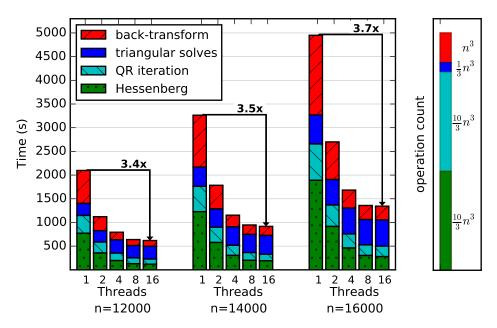

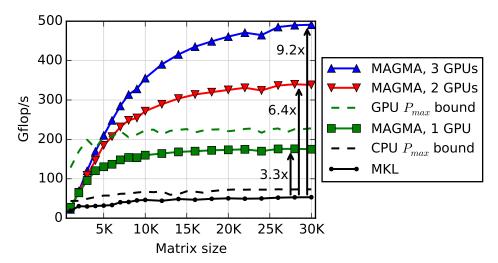

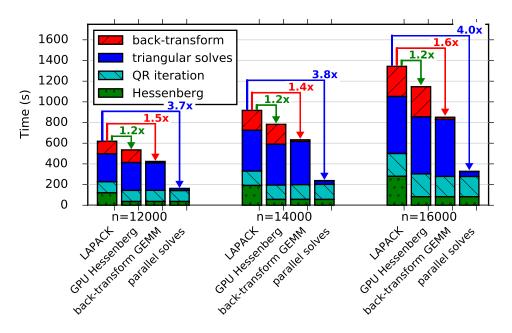

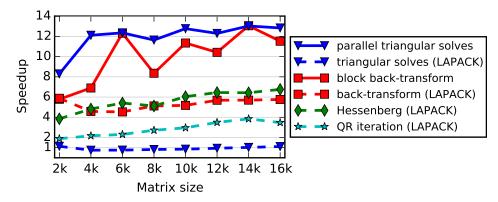

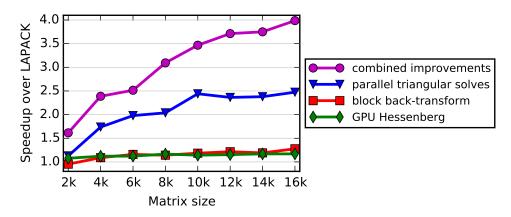

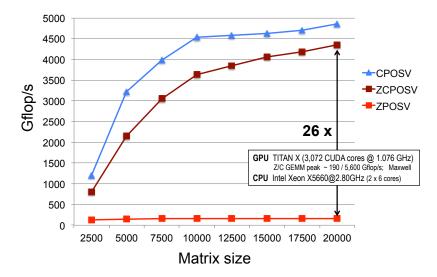

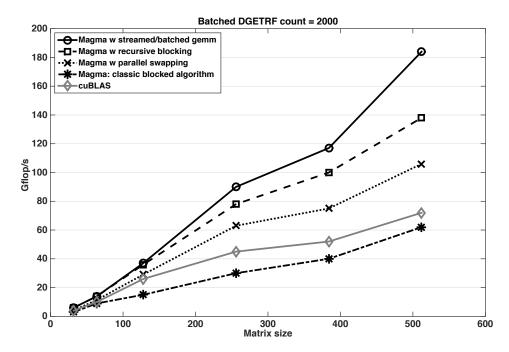

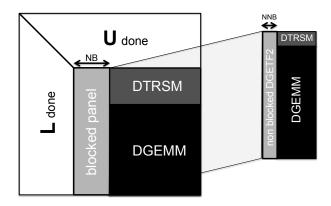

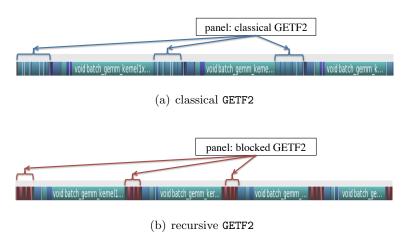

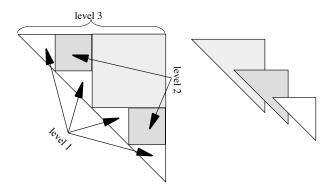

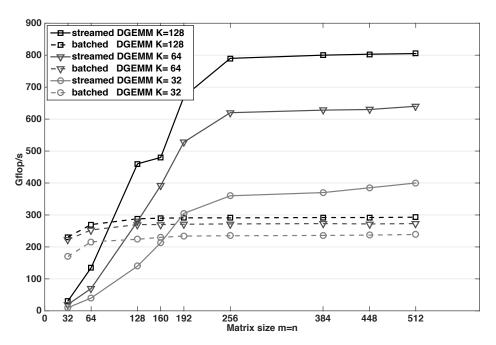

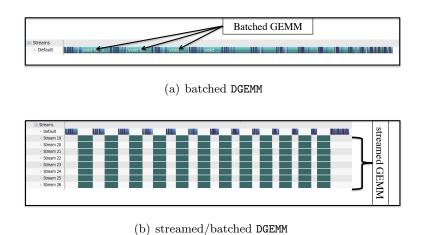

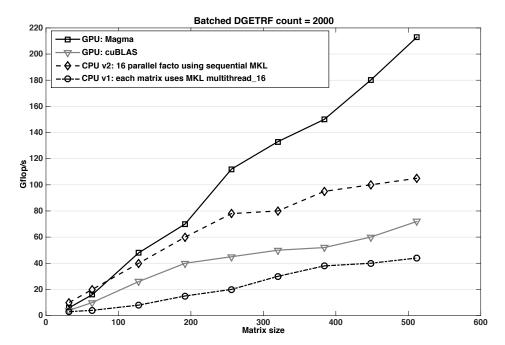

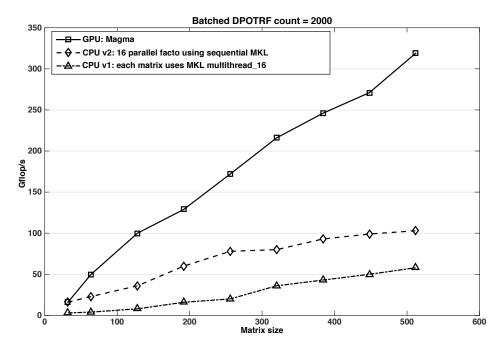

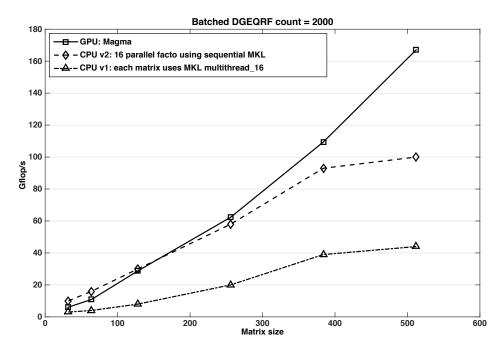

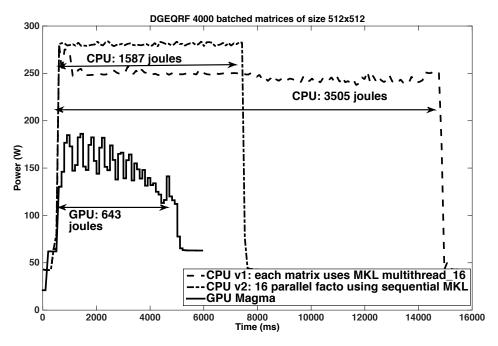

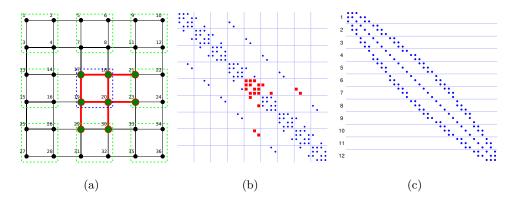

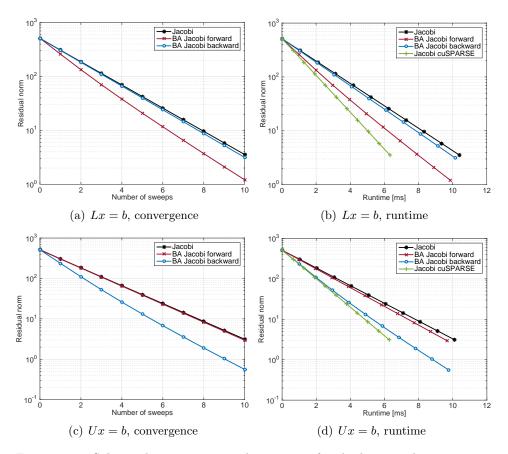

$$W^{(n,d)} = \begin{bmatrix} B_1^{(n/2^{d-1})} & 0 & \dots & 0 \\ 0 & \ddots & & \vdots \\ \vdots & & \ddots & 0 \\ 0 & \dots & 0 & B_{2^{d-1}}^{(n/2^{d-1})} \end{bmatrix} \times \dots \times B^{(n)}.$$